Pada tahun 1965, salah satu pendiri Intel, Gordon Moore, merumuskan apa yang kemudian dikenal sebagai "Hukum Moore." Selama lebih dari setengah abad, hukum ini menjadi landasan bagi peningkatan kinerja sirkuit terpadu (IC) dan penurunan biaya—fondasi teknologi digital modern. Singkatnya: jumlah transistor pada sebuah chip kira-kira berlipat ganda setiap dua tahun.

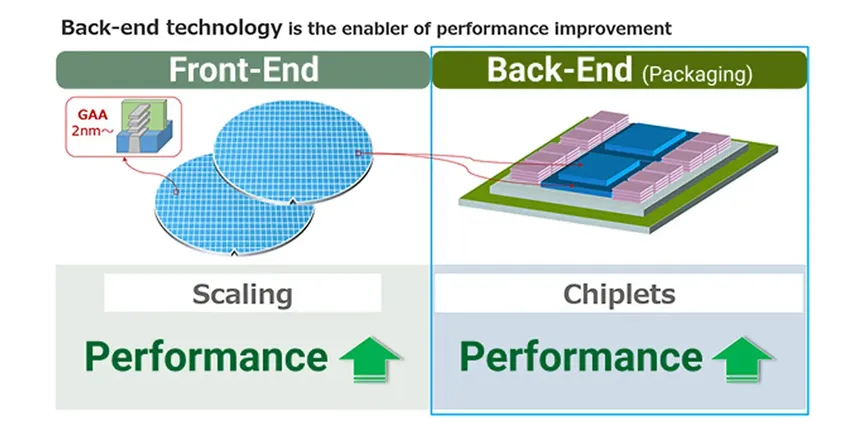

Selama bertahun-tahun, kemajuan mengikuti irama tersebut. Sekarang gambaran tersebut berubah. Pengecilan lebih lanjut menjadi sulit; ukuran fitur telah menyusut hingga hanya beberapa nanometer. Para insinyur menghadapi batasan fisik, langkah-langkah proses yang lebih kompleks, dan biaya yang meningkat. Geometri yang lebih kecil juga menurunkan hasil produksi, sehingga produksi volume tinggi menjadi lebih sulit. Membangun dan mengoperasikan pabrik terdepan membutuhkan modal dan keahlian yang sangat besar. Oleh karena itu, banyak yang berpendapat bahwa Hukum Moore kehilangan momentumnya.

Pergeseran itu telah membuka pintu bagi pendekatan baru: chiplet.

Chiplet adalah chip kecil yang menjalankan fungsi spesifik—pada dasarnya merupakan bagian dari chip monolitik yang lama. Dengan mengintegrasikan beberapa chiplet dalam satu paket, produsen dapat merakit sistem yang lengkap.

Di era monolitik, semua fungsi berada pada satu chip besar, sehingga cacat di mana pun dapat menyebabkan seluruh chip tidak berfungsi. Dengan chiplet, sistem dibangun dari "chip yang terbukti berfungsi dengan baik" (KGD), yang secara dramatis meningkatkan hasil produksi dan efisiensi manufaktur.

Integrasi heterogen—menggabungkan chip yang dibangun pada node proses yang berbeda dan untuk fungsi yang berbeda—membuat chiplet menjadi sangat andal. Blok komputasi berkinerja tinggi dapat menggunakan node terbaru, sementara memori dan sirkuit analog tetap menggunakan teknologi yang sudah mapan dan hemat biaya. Hasilnya: kinerja lebih tinggi dengan biaya lebih rendah.

Industri otomotif sangat tertarik. Produsen mobil besar menggunakan teknik ini untuk mengembangkan SoC (System-on-Chip) masa depan di dalam kendaraan, dengan target adopsi massal setelah tahun 2030. Chiplet memungkinkan mereka untuk meningkatkan skala AI dan grafis secara lebih efisien sekaligus meningkatkan hasil produksi—meningkatkan kinerja dan fungsionalitas pada semikonduktor otomotif.

Beberapa komponen otomotif harus memenuhi standar keselamatan fungsional yang ketat dan karenanya bergantung pada node lama yang sudah teruji. Sementara itu, sistem modern seperti bantuan pengemudi canggih (ADAS) dan kendaraan yang ditentukan perangkat lunak (SDV) membutuhkan daya komputasi yang jauh lebih besar. Chiplet menjembatani kesenjangan tersebut: dengan menggabungkan mikrokontroler kelas keselamatan, memori besar, dan akselerator AI yang andal, produsen dapat menyesuaikan SoC dengan kebutuhan setiap produsen mobil—lebih cepat.

Keunggulan ini meluas beyond otomotif. Arsitektur chiplet menyebar ke AI, telekomunikasi, dan domain lainnya, mempercepat inovasi di berbagai industri dan dengan cepat menjadi pilar peta jalan semikonduktor.

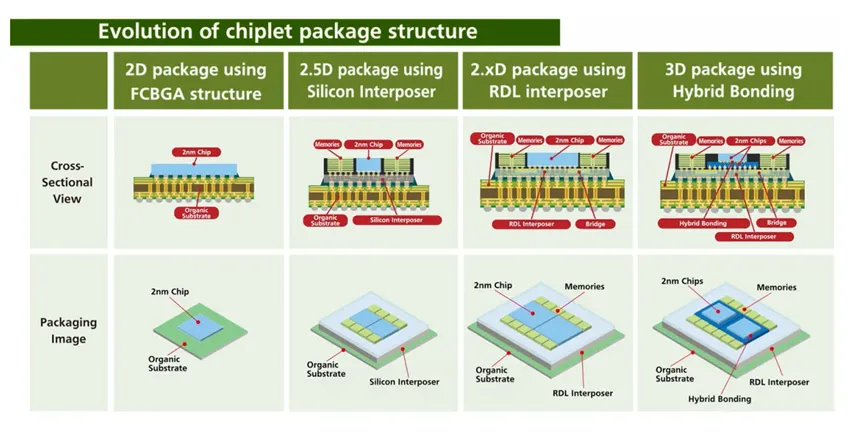

Integrasi chiplet bergantung pada koneksi antar-die yang kompak dan berkecepatan tinggi. Kunci utamanya adalah interposer—lapisan perantara, seringkali silikon, di bawah die yang mengarahkan sinyal seperti papan sirkuit mini. Interposer yang lebih baik berarti kopling yang lebih erat dan pertukaran sinyal yang lebih cepat.

Pengemasan canggih juga meningkatkan penyaluran daya. Susunan padat koneksi logam kecil antar chip menyediakan jalur yang cukup untuk arus dan data bahkan di ruang sempit, memungkinkan transfer bandwidth tinggi sekaligus memanfaatkan area kemasan yang terbatas secara efisien.

Pendekatan utama saat ini adalah integrasi 2.5D: menempatkan beberapa die berdampingan pada interposer. Lompatan selanjutnya adalah integrasi 3D, yang menumpuk die secara vertikal menggunakan vias tembus silikon (TSV) untuk kepadatan yang lebih tinggi lagi.

Kombinasi desain chip modular (memisahkan fungsi dan jenis sirkuit) dengan penumpukan 3D menghasilkan semikonduktor yang lebih cepat, lebih kecil, dan lebih hemat energi. Penempatan memori dan komputasi secara bersamaan memberikan bandwidth yang sangat besar untuk kumpulan data besar—ideal untuk AI dan beban kerja berkinerja tinggi lainnya.

Namun, penumpukan vertikal menghadirkan tantangan. Panas lebih mudah terakumulasi, sehingga mempersulit manajemen termal dan hasil produksi. Untuk mengatasi hal ini, para peneliti sedang mengembangkan metode pengemasan baru untuk menangani kendala termal dengan lebih baik. Meskipun demikian, momentumnya kuat: konvergensi chiplet dan integrasi 3D secara luas dipandang sebagai paradigma yang disruptif—siap untuk melanjutkan apa yang telah berakhir dalam Hukum Moore.

Waktu posting: 15 Oktober 2025